PB-1000/C偺撪憼儊儌儕傪512KB僞僀僾偵姺憰偡傞偙偲偱RAM梕検傪220KB x2偵奼挘偟傑偡丅

|

杮夵憿傪峴偆偲儊乕僇乕曐徹偼庴偗傜傟側偔側傝傑偡丅 傑偨億働僐儞傪夡偟偰偟傑偆偙偲傕偁傞偨傔丄幚巤偼帺屓愑擟偱偍婅偄偟傑偡丅 |

| 侾丏偼偠傔偵 |

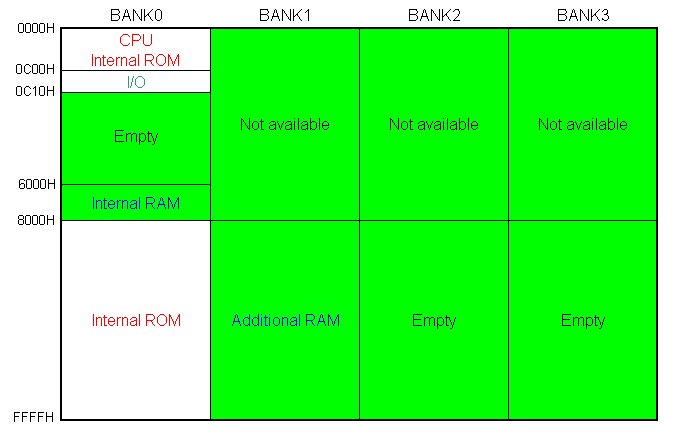

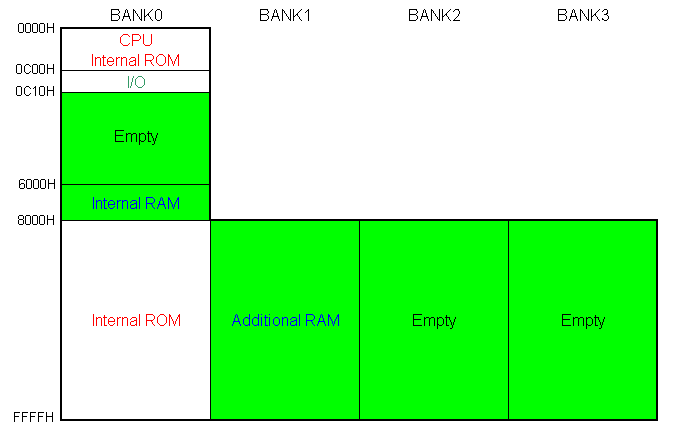

PB-1000/C偵巊傢傟偰偄傞CPU HD61700偼BANK愗傝懼偊偵傛傝嵟戝偱256KB偺傾僪儗僗嬻娫偵

捈愙傾僋僙僗弌棃傑偡偑丄PB-1000偺僔僗僥儉偱偼BANK 2,3偼巊傢傟偰偍傜偢丄傑偨IB儗僕僗僞偺

愝掕偵傛傝BANK 1-3偺0000-7FFFh偼柍岠壔偝傟偰偄傑偡丅

偦偙偱杮夵憿偱偼512KB偺S-RAM (HM628512)傪巊偄丄BANK0-3偺嬻偒椞堟偵RAM傪幚憰偟傑偡丅

偙偺夵憿偵傛傝BANK0偵栺29KB丄BANK1偐傜3偵偦傟偧傟64KB偺丄崌寁220KB偺RAM椞堟傪

儐乕僓乕僾儘僌儔儉偐傜棙梡偱偒傞傛偆偵側傝傑偡丅傑偨S-RAM偺A18偺揹埵傪愗傝懼偊傞偙偲偱

偙偺娐嫬傪2宯摑偵奼挘偟偰偄傑偡丅

| 俀丏儊儌儕憹愝偺奣梫 |

PB-1000偺儊儌儕儅僢僾偼壓婰偺傛偆偵側偭偰偄傑偡丅

偙偺嬻偒椞堟偵S-RAM傪幚憰偡傞偙偲偱丄栺220KB偺RAM椞堟傪棙梡偡傞偙偲偑壜擻偲側傝傑偡丅

| 俁丏摦嶌尨棟偲夞楬恾 |

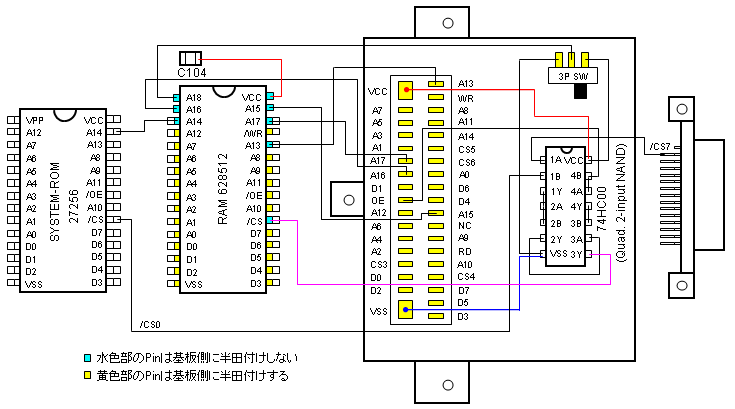

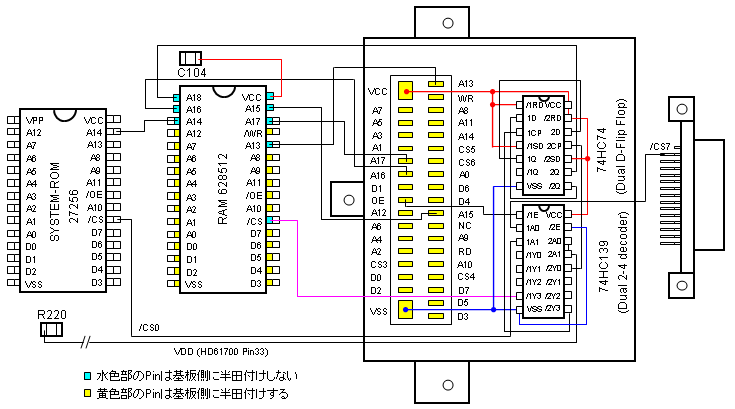

8KB偺撪晹RAM傪512KB偺S-RAM偵姺憰偟丄CPU撪憼ROM (00000-00BFFh)丄I/O億乕僩 (00C00-00C0Fh)丄

撪晹ROM (08000-0FFFFh)傾僋僙僗帪偵摦嶌偟側偄傛偆側CS怣崋傪S-RAM偵擖傟傑偡丅

岾偄側偙偲偵CPU偐傜08000-0FFFFh (CS0)偍傛傃00C00-00C0Fh (CS7)梡偺CS怣崋偑弌偰偄傞偺偱丄偙傟

偲奜晹儊儌儕梡偺CS怣崋偱偁傞OE (CPU Pin斣崋74)傪僨僐乕僪偟偰S-RAM偺CS怣崋傪嶌偭偰偄傑偡丅

側偍00000-00BFFh偼奜晹儊儌儕偺桳柍偵娭傢傜偢嫮惂揑偵CPU撪憼ROM偑慖戰偝傟傞傛偆偱偡丅

(偍偐偘偱僨僐乕僪夞楬傪戝暆偵娙慺壔偡傞偙偲偑偱偒傑偟偨)

偪側傒偵PB-1000/C偱偼儔僀僩僒僀僋儖拞偺僨乕僞偺晄掕婜娫傪CS怣崋偱儅僗僋偟偰偄傞偨傔丄傾僪儗僗慄傪

僨僐乕僪偟偨偩偗偺CS怣崋偱偼丄偙偺婜娫傕S-RAM偑僀僱乕僽儖偝傟偰晄掕僨乕僞傪彂偒崬傫偱偟傑偄傑偡丅

偦偺寢壥丄暿偺傾僪儗僗偺僨乕僞偑彑庤偵彂偒姺傢偭偨傝丄摦嶌偑晄埨掕偵側偭偨傝偡傞側偳偺晄嬶崌偑惗偠傞

偨傔丄昁偢OE怣崋偲OR(晧榑棟)傪庢傞昁梫偑偁傝傑偡丅

奺IC偺PIN攝抲偲夞楬恾傪帵偟傑偡丅CS0偼ROM偺CS抂巕偐傜丄CS7偼30pin僐僱僋僞偐傜庢傝弌偟偰偄傑偡丅

傑偨A18偺揹埵偼3P SW偱愗傝懼偊偰偄傑偡丅

| 係丏弨旛偡傞傕偺 |

杮夵憿傪峴偆偵偁偨偭偰昁梫側摴嬶偍傛傃嵽椏偱偡丅

|

僕儍儞僷慄偵偼億儕僂儗僞儞慄偺巊梡傪偍姪傔偟傑偡丅偙偺慄偼奜廃偑億儕僂儗僞儞偱旐暍偝傟偰偄傑偡偑丄

僐僥偱鄑傞偲偙偺旐暍偑梟偗偰偔傟傞桪傟傕偺偱偡丅抐柺愊傕彫偝偄偺偱丄憹愝僗儘僢僩偲儊儌儕椞堟偺搉傝

偺晹暘傕僾儔僗僠僢僋偺僇僶乕傪壛岺偡傞昁梫偑偁傝傑偣傫(崱夞偼0.26mm冇偺傕偺傪巊梡偟偰偄傑偡)丅

| 俆丏暘夝曽朄 |

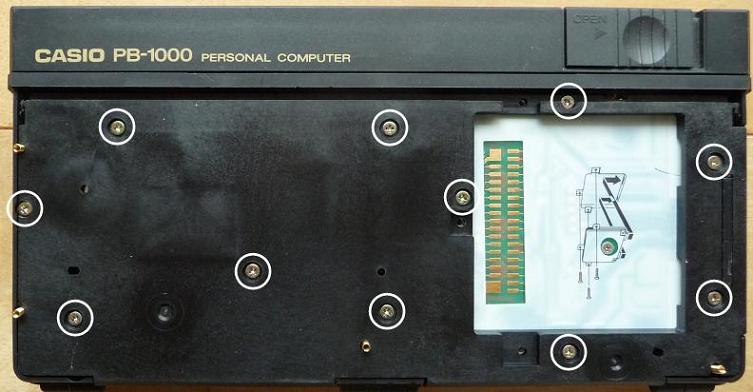

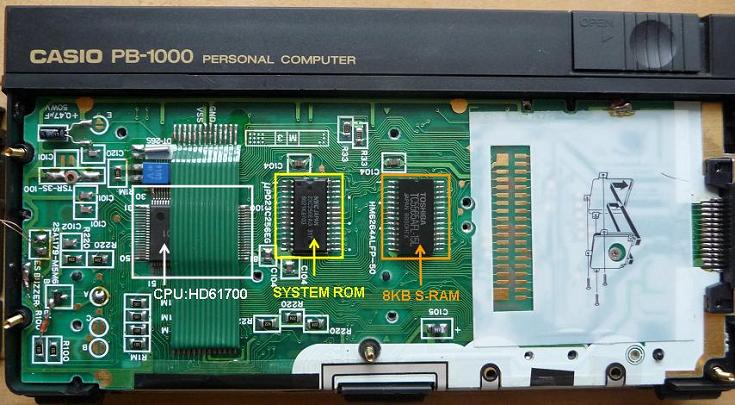

揹抮傪奜偟偨屻丄昞懁(暵偠偨忬懺)偺嬧怓偺僇僶乕傪奜偟傑偡丅師偵敀娵偱埻傫偩11杮偺僱僕傪奜偟傑偡丅

僱僕傪奜偡偲僾儔僗僠僢僋偺崟偄僇僶乕偑奜傟傑偡偑丄偙偺偲偒埑揹僽僓乕偵宷偑偭偰偄傞嵶偄僐乕僪傪愗傜側偄

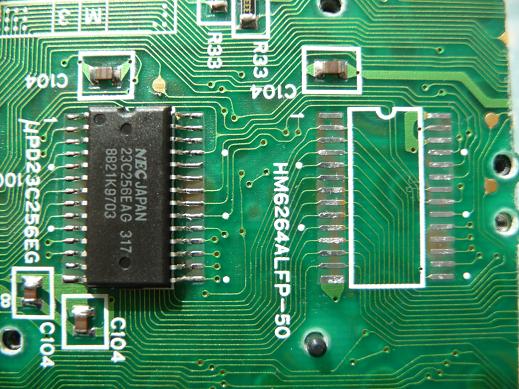

傛偆偵拲堄偟偰壓偝偄丅憹愝僗儘僢僩偺椬偵尒偊傞偺偑8KB偺S-RAM偱丄偙傟傪512KB偺S-RAM偵姺憰偟傑偡丅

| 俇丏S-RAM偺姺憰 |

崱夞偺夵憿偺嶳応偱偡丅搵嵹偝傟偰偄傞8KB偺S-RAM傪婎斅偐傜攳偑偟丄512KB偺S-RAM傪嵹偣傑偡丅

傑偢婎斅忋偺8KB S-RAM偺Pin偺敿揷傪丄敿揷媧偄庢傝慄偱彍嫀偟傑偡丅師偵偙偺Pin傪抂偐傜弴偵1杮

偢偮帩偪忋偘偰奜偟傑偡丅敿揷偛偰傪Pin偵摉偰偮偮丄惛枾僪儔僀僶乕(儅僀僫僗)摍偺嵶偄朹偱挼偹忋偘傑偡丅

Pin偺娫偵儅僀僫僗僪儔僀僶乕傪廲偵撍偭崬傒丄偦傟傪夞偟偰墶曽岦偵Pin傪挼偹忋偘傞傛偆側僀儊乕僕偱偡丅

敿揷偑梟偗偰偄側偄忬懺偱丄柍棟偵Pin傪挼偹忋偘傞偲僷僞乕儞偑攳偑傟傞偺偱廫暘拲堄偟偰壓偝偄丅

S-RAM傪奜偟偨傜僷僞乕儞忋偵巆偭偰偄傞敿揷傕偒傟偄偵彍嫀偟傑偡丅

懕偄偰512KB偺S-RAM (HM628512)偺幚憰傪峴偄傑偡丅S-RAM偺Pin偺偆偪婎斅偵敿揷晅偗偟側偄傕偺

(夞楬恾拞偺悈怓偱帵偟偨Pin)偼偁傜偐偠傔恀偭捈偖偵怢偽偟偰偍偒傑偡丅婎斅懁僷僞乕儞偺墶暆偑

僊儕僊儕側偺偱丄Pin傪嵍塃偐傜墴偟偰彮偟嫹偔偟偰偍偔偲幚憰偟傗偡偔側傝傑偡丅婎斅僷僞乕儞偲Pin偺埵抲

偑崌偭偰偄傞偐妋擣偟偨屻丄僷僞乕儞偲Pin偺埵抲偑偢傟側偄傛偆偵拲堄偟側偑傜敿揷晅偗傪峴偄傑偡丅

椬偺Pin偲僽儕僢僕偟偰傕丄峇偰偢偵敿揷媧偄庢傝慄偱梋暘側敿揷傪彍嫀偡傟偽栤戣偁傝傑偣傫丅

敿揷晅偗偑廔傢偭偨傜丄奺Pin偺摫捠妋擣傪峴偄傑偡丅偦傟偧傟偺Pin偵偮偄偰丄椬偺僔僗僥儉ROM偐

憹愝僗儘僢僩僐僱僋僞偺懳墳偡傞抂巕偲偺摫捠傪僥僗僞乕偱僠僃僢僋偟偰壓偝偄丅

| 俈丏偦偺懠晹昳偺攝抲偲攝慄 |

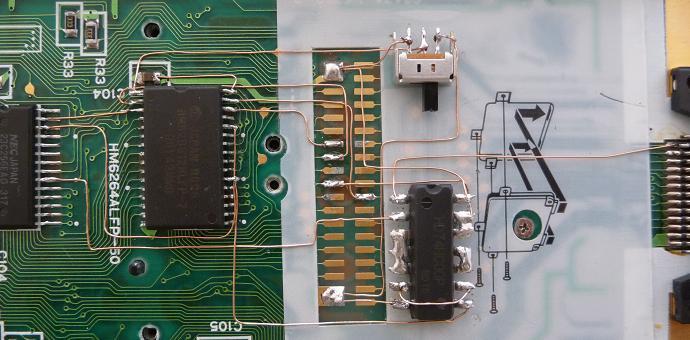

S-RAM偺姺憰偑廔傢偭偨傜丄憹愝僗儘僢僩晹暘偵3P僗僀僢僠偲儘僕僢僋IC傪椉柺僥乕僾偱揬傝晅偗傑偡丅

(儘僕僢僋IC偼偁傜偐偠傔抂巕傪抁偔愗偭偰偍偒傑偡) 偦偺屻丄夞楬恾捠傝偵攝慄嶌嬈傪峴偄傑偡丅

僕儍儞僷慄偼1杮偮側偖枅偵夞楬恾偺妋擣偲僥僗僞乕偵傛傞摫捠僠僃僢僋傪峴偭偰壓偝偄丅

慜弎偟偨傛偆偵億儕僂儗僞儞慄傪巊偆偲僾儔僗僠僢僋僇僶乕偵姳徛偣偢丄旂攳偒傕晄梫偱曋棙側偺偱偡偑丄

旂枌偺彍嫀偑晄廫暘偩偲敿揷偺擥傟惈偑旕忢偵埆偔側傝傑偡丅柺搢偱傕慄偺愭抂傪僐僥偱鄑偭偰拞偺

摵慄偵梊旛敿揷傪峴偭偰偐傜攝慄偟偨曽偑丄寢嬊嶌嬈僗僺乕僪傕忋偑傝傑偡偟丄屻乆偺僩儔僽儖傕彮側偔

側傞偲巚偄傑偡丅傑偨S-RAM偺婎斅偐傜晜偄偰偄傞Pin偑愜傟傞偲戝僟儊乕僕側偺偱丄偙偺Pin傪壗搙傕

嬋偘偨傝怢偽偟偨傝偟側偄偺偲丄戝偒側僗僩儗僗偑壛傢傜側偄傛偆偵攝慄偟偰壓偝偄丅

偱丄壓偺幨恀偑攝慄椺偱偡丅墭偄敿揷晅偗偱怽偟栿偁傝傑偣傫偑嶲峫偵偟偰壓偝偄丅

| 俉丏摦嶌妋擣 |

慡偰偺嶌嬈偑姰椆偟偨傜丄攝慄偺岆傝傗敿揷僽儕僢僕偑柍偄偐傕偆堦搙栚帇偱妋擣偟丄偝傜偵僥僗僞乕

偱摫捠僠僃僢僋傪峴偄傑偡丅栤戣偑柍偗傟偽丄杮懱傪慻傒捈偟偰摦嶌妋擣傪峴偭偰壓偝偄丅

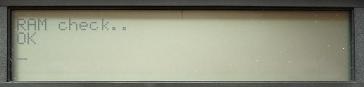

揹抮傪憰拝偟丄杮懱偺揹尮傪擖傟偨屻丄RESET丄NEWALL儃僞儞傪墴偟偰RAM傪弶婜壔偟傑偡丅

SYSTEM [EXE]傪幚峴偟偰FREE 27648 V:8191 $:1024偲側偭偰偄傟偽丄傂偲傑偢惉岟偱偡丅

揹尮偑擖傜側偐偭偨傝丄RAM偑擣幆偝傟側偄応崌偼嵞搙攝慄傪妋擣偟偰壓偝偄丅

BANK2,3偍傛傃BANK1偺0000-7FFFh偼僔僗僥儉偐傜尒偊側偄偺偱丄僠僃僢僋梡偺僾儘僌儔儉傪

弨旛偟傑偟偨丅埑弅僼傽僀儖傪夝搥屻丄check.b傪RS232C宱桼偱揮憲偟偰幚峴偟偰壓偝偄丅

僾儘僌儔儉偼00C10-05FFFh, 10000-17FFFh, 20000-2FFFFh, 30000-3FFFFh偺椞堟偵僨乕僞傪

彂偒崬傒丄偦傟偑惓忢偵撉傔傞偐偺妋擣傪峴偭偰偄傑偡丅RAM偺撉傒彂偒偑惓忢側傜"OK"偑

昞帵偝傟偰廔椆偟丄堎忢偑偁傞応崌偼"RW error"偑昞帵偝傟傞偺偱嵞搙S-RAM偺敿揷晅偗傗

攝慄傪妋擣偟偰壓偝偄丅側偍丄惓忢廔椆帪偼僠僃僢僋傪峴偭偨椞堟偼慡偰0僋儕傾偝傟傑偡丅

師偵傕偆1宯摑偺RAM偵偮偄偰傕摨偠傛偆偵弶婜壔偲僠僃僢僋傪峴偄傑偡丅

揹尮僆僼屻偵僗儔僀僪僗僀僢僠傪斀懳懁偵愗傝懼偊丄忋婰嶌嬈傪孞傝曉偟偰壓偝偄丅

| 俋丏揹尮SW偵傛傞宯摑偺愗姺偊 |

崱夞偺夵憿偱偼A18偺揹埵傪3P SW偱愗傝懼偊傞偙偲偱RAM傪2宯摑壔偟偰偄傑偡偑丄SW偑憹愝

僗儘僢僩撪晹偵偁傞偨傔愗傝懼偊偺嵺偵偄偪偄偪僇僶乕傪奜偡昁梫偑偁傝幚梡揑偱偼偁傝傑偣傫丅

偦偙偱揹尮SW偺ON/OFF偱偙傟傪愗傝懼偊傞偙偲傪専摙偟傑偟偨丅

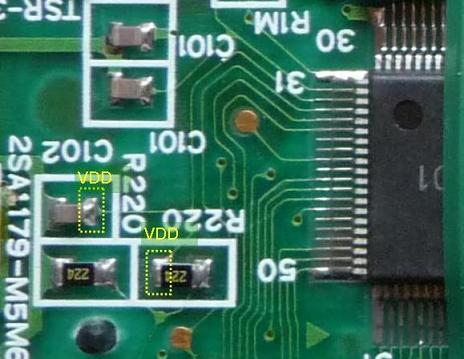

壓恾偺傛偆偵2偮偺D-FF傪慻傒崌傢偣丄偙傟傪VDD偍傛傃偦偺斀揮怣崋偱扏偒傑偡丅揹尮OFF偱

VDD怣崋偑Low仺High偵曄壔偡傞偨傔丄/Y0偑Low仺High偵愗傝懼傢傝丄1抜栚偺D-FF偵偰D仺Q

偍傛傃/Q傊偺慗堏偑惗偠傑偡丅

師偵揹尮ON偱VDD怣崋偼High仺Low偵側傞偨傔丄/Y3偑Low仺High偵愗傝懼傢傝丄2抜栚偺D-FF

偵偰D(1抜栚偺/Q)仺Q傊偺慗堏偑惗偠丄偙傟偑1抜栚偺D-FF偵栠偭偰D偑斀揮偟傑偡丅師偺揹尮

OFF偱偙偺斀揮偟偨D偑Q偵慗堏偡傞偨傔丄A18偺揹埵偑斀揮偟偰RAM偺宯摑偑愗傝懼傢傝傑偡丅

杮棃丄揹尮SW偺ON/OFF専弌偵偼SW怣崋(CPU Pin斣崋36)傪巊偆偺偑朷傑偟偄偺偱偡偑丄CPU

偺懌偵捈愙攝慄偡傞昁梫偑偁偭偰戝曄側偺偱丄VDD怣崋(CPU Pin斣崋33)傪巊偭偰偄傑偡丅

VDD怣崋偼幨恀偺傛偆偵CPU嬤偔偺R220傗C102偐傜庢傝弌偣傞偨傔丄攝慄偑懡彮妝偵側傝傑偡丅

偁偲彂偒朰傟傑偟偨偑丄HC139偑1屄梋傞偺偱丄偙傟傪CS怣崋偺僨僐乕僪梡偵巊偭偰偄傑偡丅

埲壓偵慡懱偺夞楬恾傪帵偟傑偡丅憹愝僗儘僢僩偵偼74HC00偲3P SW偺戙傢傝偵74HC74偲74HC139

傪幚憰偟傑偡丅攝慄嶌嬈偑姰椆偟偨傜丄慜復偱帵偟偨曽朄偱摦嶌妋擣傪峴偭偰壓偝偄丅

傑偨揹尮SW偺ON/OFF偱RAM偺宯摑偑愗傝懼傢傞偙偲傕妋擣偟傑偡丅

| 侾侽丏128KB RAM憹愝 |

崱夞偺512KB偺S-RAM傪巊偭偨憹愝偼媶嬌偵嬤偄傕偺偱偡偑丄僼儖傾僋僙僗偵偼IB儗僕僗僞偺

愝掕偑昁梫側偙偲傗丄SW偵傛傞愗傝懼偊傪晅壛偟偰偄傞摍丄傗傗忕挿偱偁傞偺傕帠幚偱偡丅

傑偨512KB偺S-RAM偼偦傟側傝偵抣抜傕挘傝傑偡偟丄擖庤帺懱傕崲擄偵側傝偮偮偁傞傛偆偱偡丅

偦偙偱丄偙偙偱偼傛傝埨壙側128KB偺S-RAM傪巊偭偨RAM憹愝偵偮偄偰傕徯夘偟偰偍偒傑偡丅

壓恾偺傛偆偵BANK0偺0C10-7FFFh偲BANK1偐傜3偺8000-FFFFh偵RAM傪幚憰偡傞偙偲偱丄

RAM梕検偼崌寁偱栺125KB偲側傝傑偡丅幚梡忋偼偙傟偱傕廫暘偱偟傚偆丅

128KB偺S-RAM偼廐寧揹巕捠彜偺ST儅僀僋儘惢偺傕偺偑旕忢偵埨壙偱偍姪傔偱偡丅

埲壓偵夞楬恾傪帵偟傑偡丅512KB斉偲傎傏摨偠峔惉偱偡偑丄堦晹攝慄偑娙慺壔偝傟偰偄傑偡丅

僨僐乕僪夞楬傪娙棯壔偟偰偄傞娭學偱丄BANK1-3偺0000-7FFFh偵傾僋僙僗偡傞偲8000-FFFFh偺

撪梕傪撉傒彂偒偟偰偟傑偄傑偡偑丄IB儗僕僗僞偺愝掕傪曄峏偟側偗傟偽幚奞偼柍偄偲巚偄傑偡丅

幚憰屻偺RAM僠僃僢僋偼偙偪傜偺僾儘僌儔儉傪巊偭偰壓偝偄丅

| 侾侾丏偁偲偑偒 |

PB-1000傕IB儗僕僗僞偺愝掕偱奺僶儞僋偵僼儖傾僋僙僗偱偒傞偙偲偑敪妎偟偨偨傔丄壗偲偐偙偺峀戝側嬻偒椞堟

偵RAM傪栚堦攖憹愝偱偒側偄偐偲巚偄丄崱夞偺夵憿傪幚巤偟傑偟偨丅

僐儗僋僞乕僘傾僀僥儉偲壔偟偰偄傞PB-1000/C偺撪晹RAM傪姺憰偡傞偲偄偆朶嫇偵嬤偄峴堊側偺偱丄幚峴偝傟傞

曽偼傎傏奆柍偩偲巚偄傑偡偑丄PB-1000偺儔僀僶儖婡庬(?)偱偁傞PC-E500暲傒偺RAM梕検傪20擭墇偟偱幚尰

弌棃偨偲偄偆偙偲偱丄婰帠偩偗偱傕妝偟傫偱捀偗偨傜岾偄偱偡丅

側偍夞楬偺峔惉偵摉偨偭偰偼丄嶳栮偝傫丄偁偍偝傫偵懡戝側偛嫤椡傪捀偒傑偟偨丅偁傝偑偲偆偛偞偄傑偟偨丅

2009-12-6仐Miyura

憹愝僗儘僢僩偺僐僱僋僞忣曬偼Piotr Piatek巵偺儁乕僕傪嶲峫偵偝偣偰捀偒傑偟偨丅

婰帠偼丄Miyura巵傛傝偛婑峞偟偰捀偒傑偟偨丅偛嫤椡惤偵偁傝偑偲偆偛偞偄傑偟偨丅